|

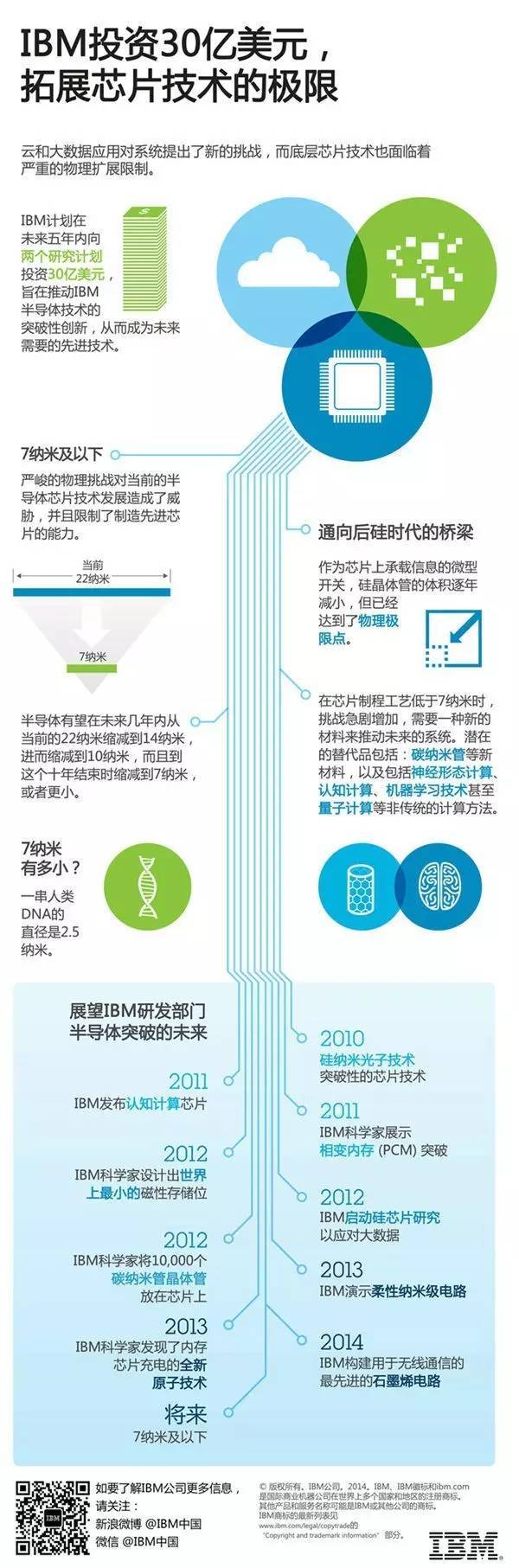

还记得在2014年,IBM曾宣布,将在未来5年投资30亿美元开展两项广泛研究及早期开发计划么?该计划以推动突破芯片技术极限,满足云计算和大数据系统的新兴需求。最近,IBM半导体和技术研究人员发表了5 篇论文,与下一代芯片开发有关。 IBM半导体和技术研究人员在近日举行的 IEEE 国际可靠性物理研讨会 (IRPS) 上发表了5 篇论文,这些论文与下一代芯片开发方面的技术和材料进步有关。

为了推动企业大规模制造 7 纳米及更短制程的芯片,IBM 团队在论文中展示了以下进步: 可提高芯片运行电压的绝缘材料; 对会给电压带来影响的芯片线路间隙中的线边缘粗糙度 (Line Edge Roughness ,LER) 变化进行建模的技术; 最有效地预筛芯片测试,从而更好地评估芯片故障率的技术; 在电压不稳定性的频率、电压、时间和温度依赖性方面,对于传统硅通道金属氧化半导体场效应晶体管 (MOSFET) 与新的硅锗 (SiGe) 通道设备中的晶体管进行比较。 论文《SiN、SiBCN 和 SiOCN 侧墙电介质的时间依赖介质击穿》全面比较了在晶体管电触点间隙中用作绝缘体的多种材料。这些侧墙电介质是芯片中最薄的绝缘体 ——在 22 纳米芯片中的测试厚度为 10 纳米,在 7 纳米芯片中约为 6 纳米。了解这些材料的寿命与芯片运行电压有何关系至关重要。 “在 7 纳米节点上,对于传统氮化硅 (SiN) 侧墙,寄生电容预计会增加到设备电容的 85%。我们需要找到一种介电常数比氮化硅更低,且兼容 CMOS 集成的材料。[我们的论文表明] 硼化硅-氮化碳 (SiBCN) 和氧化硅-氮化碳 (SiOCN) 可满足这些要求,”IBM 研究院电气特征和可靠性部门经理 James Stathis 表示。 IBM 采用 14 纳米节点技术实现了硼化硅-氮化碳 (SiBCN) ,还将用 10 纳米、7 纳米节点技术实现 硼化硅-氮化碳 (SiBCN) 。在改善电路性能和提高产能之间,硼化硅-氮化碳 (SiBCN) 是一种均衡的方法。目前也有人使用 7 纳米技术实现了氧化硅-氮化碳 (SiOCN) 。 导致绝缘体制造失败的另一个关键因素是相邻线路的间隙中的线边缘粗糙度 (LER) 和随机变化。LER 量和其他随机变化高度依赖于芯片的制造工艺。LER 影响着介质击穿的电压依赖性和时间依赖性。在 IBM 的两篇论文《LER 对 BEOL TDDB 影响的随机模型》和《一种建模线边缘粗糙度对电介质可靠性有何影响的新型整体方法》中,atv直播,提出了如何建模 LER 和其他形式的间隙变化,atv,从而正确预测电压对芯片可靠性的影响。 对开发期间制作的芯片进行测试时,在实验室中测量介质击穿(在绝缘体失效前可应用于半导体绝缘材料上的最大电压差)是一个非常耗时的过程——因为提前不知道哪些芯片的寿命最短。在论文《一种已知工艺变化的高效 MOL 和 BEOL TDDB 评估方法》中,来自 IBM 无晶圆厂可靠度小组的 IBM Systems 工程师联合 IBM 研究院工程师,开发了一种认知计算技术来最有效地进行预筛和测试排序,以显著提高测试效率。 对于晶体管的长期阈电压不稳定性,一个不同的可靠性问题是论文《Si 和 SiGe p-FinFET 中的 DC 和 AC NBTI 动力学比较》中广泛研究的主题。通过与 IIT Bombay 合作,IBM 研究院工程师对传统硅通道 MOSFET 和新型硅锗通道设备中这种现象的频率、电压、时间和温度依赖性进行了比较。 “芯片需要在正常工作条件(约 1V,且在大部分应用中最高 125C)下保持稳定,所以我们使用了更高的极限数据来外推使用条件,”Stathis 说。“此外,对于此工作,我们在最高 1MHz 的频率下进行了测试。尽管这远未达到芯片工作条件(1GHz 以上),但它的使用提供了有关 NBTI 机制的信息,而这些机制仍然存在很大争议。” 要想保证这些新的未来技术设备具有很高的可靠性,了解这些方面至关重要。

IBM研究院在此次IEEE 国际可靠性物理研讨会 (IRPS) 上发表的5 篇论文标题清单: Time Dependent Dielectric Breakdown of SiN, SiBCN and SiOCN spacer dielectric R.G. Southwick III, E. Wu, S. Mehta, J.H. Stathis A Stochastic Model for Impact of LER on BEOL TDDB R. Muralidhar , E. Wu, T. Shaw, A. Kim, B.Li, P. Mclaughlin, J. Stathis and G. Bonilla A Process-Variation-Cognizant Efficient MOL and BEOL TDDB Evaluation Method Andrew Kim, Ron Bolam, Baozhen Li, Barry Linder, and Ernest Wu Comparison of DC and AC NBTI Kinetics in Si and SiGe p-FinFETs Narendra Parihar, Richard G. Southwick, Uma Sharma (IIT Bombay), Miaomiao Wang, James H Stathis and Souvik Mahapatra (IT Bombay) A New and Holistic Modelling Approach for Impact of Line-Edge Roughness on Dielectric Reliability E. Wu, R. Muralidhar, T. Shaw, Baozhen, A. Kim, J. Stathis, and G. Bonilla 延展阅读: (责任编辑:本港台直播) |